【產(chǎn)業(yè)鏈系列文章】芯片產(chǎn)業(yè)鏈上市公司盤(pán)點(diǎn)之EDA軟件與IP核篇【產(chǎn)業(yè)鏈系列文章】芯片產(chǎn)業(yè)鏈上市公司盤(pán)點(diǎn)之EDA軟件與IP核篇

日期:

2022-01-27

導(dǎo)語(yǔ):在《芯片產(chǎn)業(yè)鏈上市公司盤(pán)點(diǎn)之IC設(shè)計(jì)篇》中�,我們?yōu)榇蠹医榻B了芯片在設(shè)計(jì)環(huán)節(jié)的流程和廠商�。芯片設(shè)計(jì)可大致分為規(guī)格制定、邏輯合成和電路布局三個(gè)環(huán)節(jié)�,如果把芯片比作一座大廈的話�����,IC設(shè)計(jì)的產(chǎn)出就是大廈的設(shè)計(jì)圖紙���,EDA軟件就是繪制這張圖紙的操作工具�,只不過(guò)相比于建筑設(shè)計(jì)�����,IC設(shè)計(jì)的復(fù)雜度要高得多。

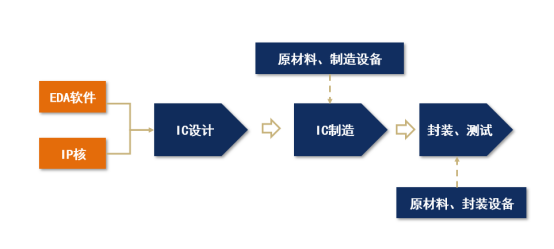

芯片的設(shè)計(jì)涉及功能�、算法、協(xié)議等等���,利用EDA軟件工具�����,IC設(shè)計(jì)工程師們能夠?qū)崿F(xiàn)從功能模塊拆解��、電路設(shè)計(jì)�、性能分析到輸出IC版圖或PCB版圖的整個(gè)過(guò)程���。一顆芯片上有數(shù)億到十億以上的晶體管�����,設(shè)計(jì)的過(guò)程要持續(xù)模擬和驗(yàn)證���,有了EDA軟件,芯片設(shè)計(jì)工作的效率可以大大提高����。同時(shí)��,EDA軟件工具在芯片制造和封測(cè)環(huán)節(jié)也有應(yīng)用��。IP核是芯片上具有較為獨(dú)立的功能模塊的成熟設(shè)計(jì)���,可編輯,可復(fù)用����,IC設(shè)計(jì)環(huán)節(jié)通常會(huì)評(píng)估整體設(shè)計(jì)成本來(lái)進(jìn)行IP的外采。IP核的模式進(jìn)一步提高了IC設(shè)計(jì)過(guò)程的整體效率����。

一、EDA軟件與IP核在全產(chǎn)業(yè)鏈中所處位置

半導(dǎo)體產(chǎn)業(yè)鏈可大致分為設(shè)計(jì)�����、晶圓制造與封裝測(cè)試三大環(huán)節(jié)���,芯片設(shè)計(jì)環(huán)節(jié)產(chǎn)出各類芯片的設(shè)計(jì)版圖,晶圓制造環(huán)節(jié)根據(jù)設(shè)計(jì)版圖進(jìn)行掩膜制作���,形成模版�����,并在晶圓上進(jìn)行加工����,封裝測(cè)試環(huán)節(jié)對(duì)生產(chǎn)出來(lái)的合格晶圓進(jìn)行切割、焊線���、塑封��,并對(duì)封裝完成的芯片進(jìn)行性能測(cè)試���。

?

在芯片設(shè)計(jì)的過(guò)程中,EDA軟件與IP核已成為廣泛使用的必備工具����。EDA是 Electronic?Design Automation的簡(jiǎn)稱,即電子設(shè)計(jì)自動(dòng)化�����。運(yùn)用EDA?設(shè)計(jì)方式形成的工具我們稱為EDA軟件�。EDA軟件使得作圖環(huán)節(jié)自動(dòng)化并對(duì)設(shè)計(jì)完成的電路圖進(jìn)行實(shí)時(shí)模擬與仿真分析,將設(shè)計(jì)師從繁瑣的畫(huà)圖作業(yè)中解放出來(lái)�,專注于理解芯片功能需求與進(jìn)行邏輯設(shè)計(jì)���;仿真分析使得芯片在設(shè)計(jì)階段盡可能實(shí)現(xiàn)貼近實(shí)際物理效果的驗(yàn)證,降低設(shè)計(jì)企業(yè)流片試產(chǎn)失敗的風(fēng)險(xiǎn)�,減少不必要的重復(fù)工作與費(fèi)用支出。

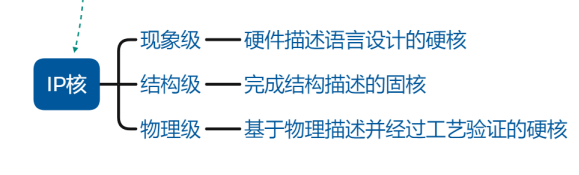

IP核指芯片設(shè)計(jì)中預(yù)先設(shè)計(jì)完成并經(jīng)過(guò)驗(yàn)證的標(biāo)準(zhǔn)化功能模塊��,通過(guò)使用IP核���,設(shè)計(jì)人員無(wú)需從0開(kāi)始對(duì)所有細(xì)節(jié)進(jìn)行重新設(shè)計(jì)����,而是借助特定的IP核經(jīng)調(diào)整后快速完成某個(gè)模塊的設(shè)計(jì)���,大幅降低了芯片設(shè)計(jì)周期與設(shè)計(jì)難度��。

?

集成電路發(fā)展早期���,產(chǎn)品結(jié)構(gòu)簡(jiǎn)單,設(shè)計(jì)師可通過(guò)手動(dòng)作圖滿足設(shè)計(jì)要求����。摩爾定律在現(xiàn)實(shí)中不斷得到驗(yàn)證�����,單位面積晶圓集成的晶體管數(shù)量不斷上升,作圖量與難度猛增推動(dòng)設(shè)計(jì)工具的不斷發(fā)展�。20世紀(jì)70年代可編程邏輯技術(shù)出現(xiàn),開(kāi)發(fā)人員開(kāi)始了將設(shè)計(jì)流程自動(dòng)化的嘗試��,硬件描述語(yǔ)言VHDL與Verilog隨之產(chǎn)生����,開(kāi)發(fā)人員使用硬件描述語(yǔ)言完成對(duì)設(shè)計(jì)邏輯的描述后將代碼輸入電子設(shè)計(jì)自動(dòng)化軟件中即可自動(dòng)生成電路圖,EDA軟件開(kāi)始出現(xiàn)并商業(yè)化�。

?

隨著集成電路設(shè)計(jì)的不斷發(fā)展,EDA軟件不僅能夠在設(shè)計(jì)環(huán)節(jié)輔助開(kāi)發(fā)者進(jìn)行設(shè)計(jì)����,亦能夠?qū)υO(shè)計(jì)完成的電路圖進(jìn)行仿真分析,模擬電路制成后的實(shí)際運(yùn)作�,使開(kāi)發(fā)者能夠在試產(chǎn)前盡可能發(fā)現(xiàn)錯(cuò)漏,從而實(shí)現(xiàn)電路的優(yōu)化設(shè)計(jì)���。芯片設(shè)計(jì)完成后的試產(chǎn)環(huán)節(jié)(流片)意義重大�����,流片失敗意味著返工重新進(jìn)行設(shè)計(jì)與再一次支付高昂的流片費(fèi)用���。EDA軟件也在制造環(huán)節(jié)中得到應(yīng)用�,晶圓制造商通過(guò)EDA軟件對(duì)自身的產(chǎn)品進(jìn)行建模并將模型發(fā)送至各芯片設(shè)計(jì)企業(yè)����,使芯片設(shè)計(jì)企業(yè)能夠?qū)⒋S商的技術(shù)工藝特點(diǎn)考慮到設(shè)計(jì)中,加強(qiáng)了芯片產(chǎn)業(yè)鏈上下游的協(xié)同����。在EDA軟件迅速發(fā)展的同時(shí),芯片設(shè)計(jì)的另一重要工具IP核也得到了廣泛應(yīng)用���。隨著集成電路功能復(fù)雜化與產(chǎn)品推新周期縮短的趨勢(shì)顯現(xiàn)����,半導(dǎo)體領(lǐng)域出現(xiàn)獨(dú)立IP廠商�,獨(dú)立IP廠商為芯片設(shè)計(jì)企業(yè)直接提供經(jīng)過(guò)驗(yàn)證的IP模塊庫(kù),設(shè)計(jì)企業(yè)的開(kāi)發(fā)者無(wú)需從頭設(shè)計(jì)�����,而是直接調(diào)用特定功能模塊�����,經(jīng)過(guò)調(diào)整后便可實(shí)現(xiàn)所需功能�,芯片設(shè)計(jì)企業(yè)可將其余人力物力傾斜于產(chǎn)品定義、系統(tǒng)架構(gòu)�、市場(chǎng)營(yíng)銷等環(huán)節(jié)。

為了更好地理解IP核的邏輯��,我們可將IP核類比為汽車生產(chǎn)過(guò)程的動(dòng)力系統(tǒng)���、轉(zhuǎn)向系統(tǒng)�����、懸架系統(tǒng)�����、車身系統(tǒng)等部分�,主機(jī)廠并不進(jìn)行所有汽車零部件的生產(chǎn)�����,而是將大部分零部件外包給一級(jí)與二級(jí)供應(yīng)商�,自身則專注于動(dòng)力系統(tǒng)與組裝技術(shù)的研發(fā),并在生產(chǎn)過(guò)程中將汽車的所有零部件進(jìn)行協(xié)同優(yōu)化與系統(tǒng)集成。IP模塊庫(kù)的使用極大降低了設(shè)計(jì)的難度與時(shí)間周期��,芯片設(shè)計(jì)由電路設(shè)計(jì)轉(zhuǎn)變?yōu)橄到y(tǒng)設(shè)計(jì)��。

按開(kāi)發(fā)程度進(jìn)行分類����,IP核的分類如下圖所示,開(kāi)發(fā)程度越高的IP核�����,后期可編輯程度越低�����,而可預(yù)見(jiàn)性更高�����。

?

二�、EDA軟件、IP核主要上市公司匯總

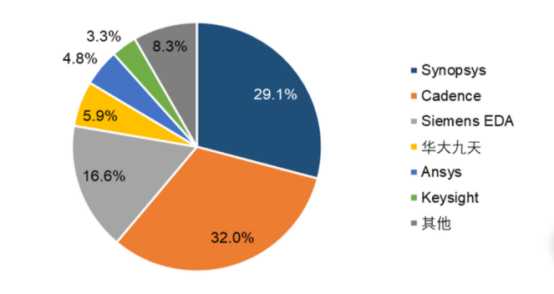

EDA與IP核行業(yè)均為集中度極高的寡頭壟斷市場(chǎng)�,根據(jù)賽迪智庫(kù)2020年統(tǒng)計(jì)數(shù)據(jù),國(guó)際三巨頭Synopsys���、cadence與西門(mén)子旗下子公司Mentor?Graphic占有國(guó)內(nèi)78%的市場(chǎng)份額����,海外EDA軟件企業(yè)占有國(guó)內(nèi)至少86%的市場(chǎng)份額。在IP核領(lǐng)域�,ARM�����、Synopsys與Cadence占有全球66%的市場(chǎng)份額�����,國(guó)內(nèi)龍頭芯原股份在全球市占率為2%��。

?

數(shù)據(jù)來(lái)源:中商產(chǎn)業(yè)研究院目前��,國(guó)內(nèi)EDA軟件與IP核相關(guān)上市公司分別有華大九天��、概倫電子與芯原股份�,三家公司均于2021年在科創(chuàng)板上市。

公司簡(jiǎn)稱 | 股票代碼 | 主營(yíng)業(yè)務(wù) | 類別 |

華大九天 | A21150.SH | 公司主要產(chǎn)品包括模擬電路設(shè)計(jì)全流程EDA工具系統(tǒng)��、數(shù)字電路設(shè)計(jì)EDA工具�����、平板顯示電路設(shè)計(jì)全流程EDA工具系統(tǒng)和晶圓制造EDA工具等EDA工具軟件產(chǎn)品。 | EDA軟件:模擬電路設(shè)計(jì)全流程EDA軟件����、數(shù)字電路設(shè)計(jì)EDA軟件、平板顯示電路設(shè)計(jì)全流程EDA軟件�����。晶圓制造EDA工具 |

概倫電子 | 688206.SH | 公司主要產(chǎn)品及服務(wù)包括制造類EDA工具�����、設(shè)計(jì)類EDA工具���、半導(dǎo)體器件特性測(cè)試儀器和半導(dǎo)體工程服務(wù)等�, | EDA軟件:設(shè)計(jì)和制造類EDA軟件 |

芯原股份 | 688521.SH | 公司是一家依托自主半導(dǎo)體IP����,為客戶提供平臺(tái)化、全方位�����、一站式芯片定制服務(wù)和半導(dǎo)體IP授權(quán)服務(wù)的企業(yè)。 | IP核 |

三��、芯片設(shè)計(jì)行業(yè)主要上市公司財(cái)務(wù)概覽

國(guó)內(nèi)EDA與IP核領(lǐng)域企業(yè)的發(fā)展面臨較大困難���,除缺乏資金與人才外更缺乏下游產(chǎn)業(yè)的支持����。芯片設(shè)計(jì)的每一環(huán)節(jié)高度關(guān)聯(lián)��,海外三巨頭經(jīng)過(guò)長(zhǎng)時(shí)間發(fā)展已形成覆蓋面完整的工具鏈條����,使下游廠商對(duì)其具有極大的黏性�����。國(guó)內(nèi)企業(yè)目前僅能提供部分領(lǐng)域產(chǎn)品���,獲得客戶較難���,因而更難獲得足夠的下游數(shù)據(jù)改良迭代自身產(chǎn)品,與三巨頭的差距不斷增大���。國(guó)內(nèi)半導(dǎo)體IP巨頭芯原股份依舊處于虧損狀態(tài)��。

公司簡(jiǎn)稱 | 2021年上半年?duì)I業(yè)收入(億元) | 2021年上半年毛利率 | 動(dòng)態(tài)市盈率(2022年1月11日) |

華大九天 | 1.82 | 88.46%(全產(chǎn)品) | / |

概倫電子 | 0.54 | 100% | 717.16 |

芯原股份 | 2.14 | 96.69% | 虧損 |

四�����、芯片設(shè)計(jì)行業(yè)主要上市公司近期動(dòng)態(tài)

?

公司簡(jiǎn)稱 | 2021年動(dòng)向 |

華大九天 | 已過(guò)會(huì)�,預(yù)計(jì)募資25.51億元,其中5億元用于電路仿真及數(shù)字分析優(yōu)化EDA工具升級(jí)項(xiàng)目����;2.9億元用于模擬設(shè)計(jì)及驗(yàn)證EDA工具升級(jí)項(xiàng)目;4.3億元用于面向特定類型芯片設(shè)計(jì)的EDA工具開(kāi)發(fā)項(xiàng)目�����;5.6億元用于數(shù)字設(shè)計(jì)綜合及驗(yàn)證EDA工具開(kāi)發(fā)項(xiàng)目 |

概倫電子 | 公司成功上市募資12.09億元���,其中3.8億元用于建模及仿真系統(tǒng)升級(jí)建設(shè)項(xiàng)目����;3.4億元用于設(shè)計(jì)工藝協(xié)同優(yōu)化��;2.5億元用于建設(shè)研發(fā)中心��;1.5億元用于投資并購(gòu);剩余補(bǔ)充流動(dòng)資金 |

芯原股份 | 公司開(kāi)發(fā)的基于高性能總線架構(gòu)和FLC終極內(nèi)存/緩存技術(shù)的可復(fù)用的ASIC軟硬件平臺(tái)在2021年上半年完成流片�����。 |